Niveaux de programmation

– Du plus bas niveau (1) au plus abstrait (6)

1) Impulsions électriques : 0 et 1 dans portes/composants

2) Micro-instructions

– Séquencement via unité de commande, chemin de données

3) Micro-opérations internes

– Traduction opérations complexes CISC en µOP de type RISC

4) Langage machine

– Codage binaire des opérations : code opération + codes opérandes

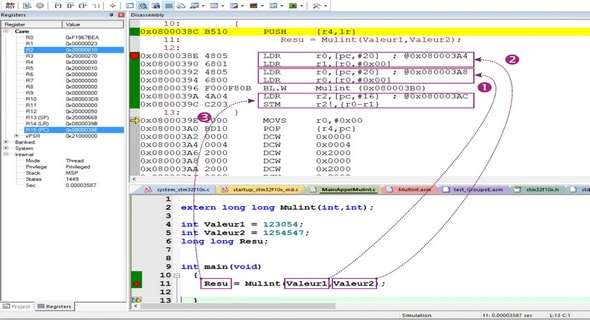

5) Assembleur

– Langage machine avec codes mnémotechniques à la place des codes opération en binaire

Jeu d’instructions

– Jeu d’instruction

– Ensemble des instructions machine (et donc assembleur) qu’un processeur sait exécuter

– Deux grandes familles de jeu d’instruction

– CISC : Complex Instruction Set Computing

– Instructions nombreuses et pouvant être complexes et de taille variab

– Peu de registres

– Exemple : Intel x86

– RISC : Reduced Instruction Set Computing

– Intructions limitées et simples et de taille fixe

– Adressage mémoire : chargement/rangement (que via des registres)

– Nombre relativement importants de registres

Architecture Intel x86

– Architecture Intel x86

– Date du processeur 8086 en 1978

– … et toujours en vigueur aujourd’hui dans les processeurs Intel et AMD

– Données sur 16 bits

– Adresses mémoire sur 20 bits : 1 Mo addressabe

– 8 registres généraux de 16 bits

– Architecture vieillisante

– Trop peu de registres et de taille trop petite

– Evolution de cette architecture avec les nouvelles gammes de processeurs Intel et compatibles

Registres x86

– 8 registres 16 bits généraux

– AX, BX, CX, DX, DI, SI, BP, SP

– Chaque registre peut avoir une fonction particulière implicite selon l’instruction utilisée

– AX : accumulateur

– BX : base (adresse mémoire)

– CX : compteur

– DX : donnée, entrées/sorties

– SI : index source

– DI : index destination

– BP : base de la pile

– SP : pointeur sur le sommet de la pile

Segments et adresses mémoire

– Bus d’adresse de l’architecture x86

– 20 bits soit 1 Mo de mémoire adressable

– Mais registres n’ont que 16 bits

– 64 Ko de mémoire adressable

– Pour avoir des adresses mémoire sur 20 bits avec des registres de 16 bits

– On combine 2 registres

– Le premier donne l’adresse de base d’un segment

– Le second donne le déplacement dans ce segment

– Segment = zone mémoire de 64 Ko

…

Cours architecture des ordinateurs (275 KO) (Cours PDF)