Synthétiseur de fréquences à division entière

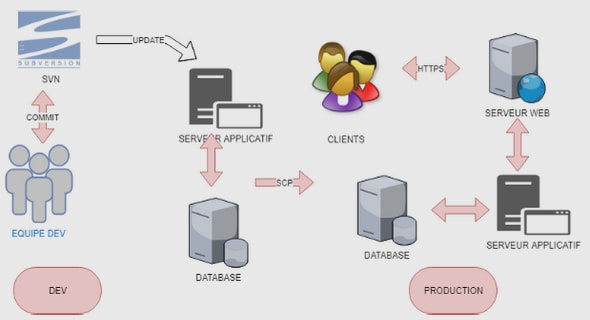

L’architecture classique d’un synthétiseur de fréquence à division entière utilisant une boucle à verrouillage de phase (PLL) est illustrée sur la figure II.1. Cette architecture est composée des éléments suivants [16], [17]: un comparateur phase-fréquence suivi d’une pompe de charge, un filtre de boucle, un oscillateur contrôlé en tension et un diviseur de fréquence. La sélection du canal à synthétiser se fait en agissant sur le rapport de division N, comme le montre la figure II.1. Il consiste en un asservissement de la phase et de la fréquence d’un signal de sortie sur la phase et la fréquence d’un signal d’entrée de référence, à un facteur N près, N étant le rang de division de la boucle de retour. Ainsi, lorsque la boucle est verrouillée, la fréquence du signal de sortie out F est proportionnelle à la fréquence du signal d’entrée 0 F suivant la relation, 0 F M F N out (II.1) Pour réaliser un synthétiseur de fréquences, deux possibilités sont offertes [18], [19]: Les synthétiseurs de fréquences fractionnaires utilisent la deuxième solution pour générer toute une plage de fréquence. Avec ce type de synthétiseur, la valeur de la fréquence de référence ref F est fixée par le pas de fréquence de sortie souhaité.

La fréquence de coupure du filtre de boucle qui définit la bande passante de la PLL, doit être suffisamment faible pour filtrer les raies parasites résultantes du processus de comparaison (comparateur de phase et pompe de charges). Dans les applications cellulaires actuelles, pour lesquelles le pas de fréquence est de l’ordre de la centaine de kHz, les bandes passantes des PLLs à division entière sont faibles et entraînent des temps d’établissement relativement élevés, de l’ordre de plusieurs centaines de microsecondes. Il y a un compromis à faire entre le temps de réponse du synthétiseur de fréquences à division entière et son pas de résolution fréquentiel. Deux choix s’offrent aux concepteurs : – Soit la réduction du temps d’accrochage : un meilleur temps d’accrochage est obtenu par un élargissement de la bande passante de la boucle. Pour conserver une atténuation suffisante des raies parasites de comparaison, la fréquence de référence doit être également augmentée ce qui permet d’élargir la bande passante de la PLL et donc d’abaisser ainsi le plancher de bruit de phase. La combinaison d’une bande passante plus large et d’un plancher de bruit de phase plus faible permet d’obtenir un bruit de phase global plus faible. En contrepartie, le pas de fréquence est augmenté en même temps que la fréquence de référence. – Soit la diminution du pas de fréquence : pour obtenir un faible pas de fréquence, il suffit de diminuer la fréquence de référence. Pour atténuer les raies parasites de comparaison, la bande passante de la boucle doit également être réduite. Ceci engendre une augmentation du temps d’accrochage et une hausse du plancher de bruit de phase. La combinaison de la faible bande passante et du plancher de bruit élevé détériore le bruit de phase global.

Comparateur phase- fréquence (PFD)

Le détecteur de phase est un circuit à deux entrées qui donne une tension de sortie proportionnelle au déphasage entre les deux fréquences d’entrée. Un exemple du comparateur de phase classique est représenté sur la figure II. 2. Un comparateur phase-fréquence génère en sortie deux signaux (Sup et Sdown). Lorsque l’entrée E1 est en avance de phase sur l’entrée E2 alors Sup est au niveau haut et Sdown au niveau bas. Lorsque E1 est en retard de phase sur E2, on obtient la configuration inverse, c’est-à-dire Sup au niveau bas et Sdown au niveau haut. Lorsque les deux signaux sont synchronisés, Sup et Sdown sont tous les deux au niveau bas. La détection de l’avance ou du retard de phase d’un signal par rapport à un autre se fait sur les fronts montants. La figure II.3 illustre le principe de fonctionnement du PFD. Figure II.2. Circuit d’un comparateur numérique de phase-fréquence. Figure II.3. Diagrammes des différents signaux. Plusieurs phénomènes sont à prendre en compte lors de la conception d’un comparateur de phase et de fréquence. D’abord, si l’erreur de phase varie très rapidement, il peut y avoir perte du verrouillage de la boucle. Ensuite, un autre problème qui peut intervenir sur la qualité d’un comparateur de phase et de fréquence est l’existence de « zones mortes » qui correspondent au gain nul de la pompe de charge. Ce phénomène se produit lorsque le déphasage, très faible, entre la sortie du VCO et la référence n’engendre pas d’impulsion de courant du fait du temps de réponse des circuits électroniques. Le gain de la boucle étant nul, la phase du VCO n’est plus asservie par la boucle et le bruit de phase de la PLL augment

Le filtre de boucle

Le filtre de boucle a pour fonction de filtrer la sortie du circuit de pompe de charge afin d’éliminer les composantes hautes fréquences sur la tension de contrôle du VCO. De par le choix des valeurs des composants qui le constituent, le filtre de boucle est l’élément qui garantit la stabilité de la PLL [20]. Les paramètres tels que le temps d’établissement, la bande passante et le bruit de phase dépendent de ce filtre. Les sorties du détecteur de phase sont associées en un seul signal par la pompe de charge. Ce signal résultant est ensuite appliqué à un filtre passe-bas pour que la tension de sortie du comparateur de phase (détecteur de phase) ne varie pas trop rapidement. Car si la tension d’erreur varie trop rapidement la tension de correction envoyée à l’oscillateur (VCO) fera en sorte que la fréquence de sortie de l’oscillateur sera soit trop haute ou trop basse et qu’il faudra ramener la fréquence trop rapidement et on dépassera la valeur dans l’autre direction. Donc en ralentissant la tension de correction par une capacité, on s’assure que l’ajustement se fait lentement et pas trop fortement. Il existe trois types de filtres de boucle du second ordre: passif RC, actif RC et actif PI (proportionnel intégral) [21].

Le filtre passif RC du second ordre est le plus employé. L’utilisation d’un filtre passif évite l’injection dans la PLL de la contribution en bruit d’un amplificateur opérationnel inhérent au filtre actif. La conception de la plupart des PLLs s’appuie donc sur une structure passive RC [22], [23]. La figure I.6 présente un filtre passif du deuxième ordre. Le filtre de la boucle est une impédance complexe en parallèle avec la capacité d’entrée du VCO. On note que la capacité parallèle C1 est recommandée pour éviter les pas en tension discrets au port de contrôle du VCO dû aux changements instantanés dans le courant de sortie de la pompe de charge. On note que le filtre passe-bas est la partie essentielle du circuit à boucle de réaction à verrouillage de phase, qui convertit la sortie du comparateur de phase en tension continue pour le contrôle du VCO. Parce qu’on y retrouve une constante de temps, le verrouillage n’est pas instantané et la fréquence de sortie verrouille à la valeur moyenne de la fréquence de référence. Cette caractéristique permet d’obtenir une fréquence de sortie propre, à partir de fréquences d’entrée de référence contenant du bruit. Le filtre passe-bas crée un déphasage entre Fout et F0. Ce déphasage constitue la tension qui stabilise la fréquence du VCO.

Elaboration et évaluation des performances du filtre de boucle

Cette partie concerne l’élaboration d’un filtre de boucle passif pour des synthétiseurs de fréquences utilisant un détecteur de phase-fréquence et une pompe de charge comme ceux de la série d’Analog Devices. La conception d’un filtre passif de deuxième ordre est discutée en détail ainsi que des filtres d’ordre supérieur. La configuration standard du filtre passif de deuxième ordre de la pompe de charge de la PLL est montrée sur la figure II.6. Le filtre de boucle est une impédance complexe en parallèle avec l’entrée du VCO. Rappelons que la capacité parallèle C1 est recommandée pour éviter les pas discrets de tension au port du contrôle du VCO dû aux changements instantanés dans le courant de sortie de la pompe de charge. Le filtre de boucle contrôle le signal de commande du VCO. La plage de capture, ou plage d’accrochage (pull-in range), dépend de la bande passante et de l’ordre du filtre de boucle ainsi que du gain de boucle, lui-même fonction du gain du VCO et du détecteur de phase. Toutefois, il est possible d’assimiler, en première approche, la plage de capture à la bande passante du filtre de boucle. Le rôle de ce filtre est d’assurer la stabilité de la boucle de phase et de filtrer les résidus de la fréquence de comparaison. Le choix du filtre est lié à ces différents paramètres.

Plus la fréquence de coupure sera basse meilleure sera l’atténuation des signaux résiduels. Mais la boucle sera également beaucoup plus lente à se stabiliser, d’où un temps d’établissement excessif pour un système devant effectuer des sauts de fréquence importants entre l’émission et la réception. Idéalement, le filtre de boucle devrait être intégré dans le même circuit que le comparateur de phase. En fait ceci se heurte à plusieurs difficultés. Le filtre de boucle ne doit pas ajouter de bruit. On a donc intérêt à le réaliser à l’aide de composants passifs plutôt qu’actifs. D’autre part, en intégrant totalement, on est limité dans le choix des valeurs de composants, les capacités ne pouvant dépasser quelques dizaines de pF. Enfin, un filtre intégré risque d’être parasité par les autres signaux circulant dans le circuit. Cependant, le filtre de boucle sera différent pour chaque PLL afin qu’il puisse assurer des temps d’accrochage, une stabilité et un filtrage du bruit du détecteur de phase convenables. Une méthode de conception du filtre utilise le gain de la boucle ouverte et la marge de phase pour déterminer les valeurs des composants. La localisation du point de déphasage minimum où le gain de la boucle ouverte est égal à l’unité assure la stabilité de la boucle (figure II.10).

La marge de phase Øp est définie comme étant la différence entre 180° et la phase de la fonction de transfert en boucle ouverte à la fréquence p correspondant au gain égal à 0 dB. Pratiquement, la marge de phase est choisie entre 30° et 70° . Autrement, lorsqu’on choisit une marge de phase plus élevée, il en résulte une très haute stabilité pendant un temps de réponse plus lent de boucle et moins d’atténuation de Fref. Pour cela, ce principe de base commun nous a guidé à commencer notre conception par une marge de phase de 45°. Les seules valeurs des composants qui doivent être déterminées concernent le pole passe-bas supplémentaire. Puisque ces valeurs sont déterminées à partir des équations (II.20), (II.21), elles sont quelque peu arbitraires. Toutefois il n’est pas prudent d’avoir une capacité C3 de valeur égale ou supérieure à celles des autres capacités, du fait que le principe de base pour de telles applications est de choisir C3 C1/10, autrement la constante du temps T3 agira sur les autres pôles primaires du filtre. De même, on choisit la valeur de R3 au moins deux fois la valeur de R2. Le choix de C3 dépend aussi de la capacité d’entrée de la diode varicap du VCO qui s’ajoutera en parallèle.

Conclusion générale

La génération et la transposition de fréquence sont deux fonctions qui apparaissent comme des éléments essentiels particulièrement critiques dans une chaîne d’émission/réception radio. En effet, compte tenu des problèmes d’encombrement spectral liés à la rareté des fréquences disponibles dans le spectre radio, les caractéristiques de bruit de phase pour l’oscillateur doivent satisfaire des spécifications de plus en plus contraignantes. Les systèmes actuels privilégient donc, au niveau des besoins en génération de fréquence, les sources synthétisées très stables et intégrables à faible coût. En ce qui concerne le mélangeur, les contraintes classiques de gain, de facteur de bruit et d’intégration à faible coût sont également à prendre en compte. Les boucles à verrouillage de phase (PLL) jouent un rôle majeur dans le domaine des communications mobiles. La PLL est utilisée comme une partie essentielle du synthétiseur de fréquences en fonctionnant comme un détecteur cohérent par la correction continue de la fréquence de sortie de l’oscillateur contrôlé en tension (VCO). Cette correction est réalisée en utilisant l’erreur de phase entre la fréquence de comparaison et la fréquence de contre réaction (la fréquence de sortie divisée par N).

Les travaux présentés dans ce manuscrit explorent la conception de simple architecture du synthétiseur de fréquence à base de PLL pour les communications radio mobiles LTE/LTE-Advanced. Dans ce mémoire, on a pu qualifier le modèle ADF4106 pour des applications radio mobiles 4 G. Ce modèle a été conçu en utilisant le logiciel professionnel ADISimPLL de la firme Analog Devices. Cette conception nous a fourni toutes les informations sur les principales caractéristiques et performances du système y compris les raies de références à des multiples de la fréquence de comparaison. Pour notre application, le signal de sortie obtenu est d’une densité de bruit de -137 dBc/Hz à une excentration de 5MHz de la fréquence centrale, un temps de verrouillage de l’ordre de 24,85 μs, une erreur de phase RMS de 0.28 degrés. Ces caractéristiques montrent bien l’importance de ce circuit dans les systèmes de communications modernes de la quatrième génération (4G). Le synthétiseur de fréquences conçu n’a pas pu être réalisé en pratique à cause de la non disponibilité de ces composants sur le marché national. Cette étude permettra la conception de nouveaux synthétiseurs de fréquences fonctionnant à des fréquences plus élevées en suivant la même démarche pouvant être exploités dans les émetteurs /récepteurs du système 5 G.

Résumé |