Cours architecture des ordinateurs hiérarchie des mémoires par performance, tutoriel & guide de travaux pratiques en pdf.

ARCHITECTURE DU PROCESSEUR

Comme on l’a déjà précisé, c’est le processeur qui exécute les instructions constituants le programme. Cette tâche nécessite plusieurs interventions qui sont classées en général dans deux blocs différents. Le premier bloc constitue l’unité de contrôle qui va amener, une par une les instructions à partir de la mémoire centrale, analyse chaque instruction, charge éventuellement les donnée nécessaires à son exécution dans les registres et déclenche son exécution par le deuxième bloc appelé Unité Arithmétique et Logique (ALU) en lui envoyant les signaux électriques correspondant à l’opération désirée. La figure 2.1 illustre l’architecture simplifiée d’un processeur.

L’UNITE DE CONTROLE

L’unité de contrôle est l’unité qui supervise le déroulement de toutes les opérations, elle contient principalement :

• Une horloge qui va permettre la synchronisation des opérations.

• Un séquenceur qui génère les signaux de commande et gère le séquencement des opérations.

• Un registre d’instruction RI où est stockée l’instruction en cours d’exécution.

• Un registre dit compteur ordinal CO ( PC : program counter) qui contient l’adresse mémoire où est stockée la prochaine instruction à charger. Au début de l’exécution d’un programme, le CO est initialisé par le système d’exploitation à l’adresse mémoire où est stockée la première instruction du programme. Le compteur ordinal est incrémenté chaque fois qu’une instruction est chargée dans le CPU.

• Un décodeur qui va « décoder » l’instruction contenue dans RI et générer les signaux correspondant et les communiquer aux autres unités (séquenceur).

L’UNITE ARITHMETIQUE ET LOGIQUE A B

L’ALU contient tous les circuits électroniques qui

réalisent effectivement les opérations désirées. Ces

opérations sont principalement l’addition, la soustraction, A3 A2 A1 A0 B3 B2 B1 B0 Re

la multiplication, la division ainsi que les opérations C C0

logiques comme la négation, ET, OU, OUX et les 1 C Rs

opération de décalage de bits. Le schéma de la figure 2.2 C2 S3 S2 S1 S0 OVR

montre un exemple (74LS382) d’ALU. Les nombres A et

B constituent les deux opérandes. Le nombre C constitue S

le code de la fonction à réaliser. Le nombre S est le

résultat de l’opération. Re et Rs sont les retenues

Structure et Technologie des Ordinateurs par A. OUMNAD 8

entrante et sortante. OVR indique qu’il y a un dépassement. Le tableau ci-dessous résume le fonctionnement de cette ALU.

LES REGISTRES

Les registres sont des unités de mémorisation d’un mot machine dont la taille dépend des processeurs, on trouve des registres de 8 bits, 16 bit et 32 bits. Certains registres servent à stocker les codes d’instruction, d’autres servent à stocker les donnés constituant les opérandes et les résultats des opérations. D’autres servent à stocker les adresses permettant d’accéder aux opérandes sur la mémoire centrale.

• PC : (program counter) ou Compteur Ordinal CO. C’est lui qui contient l’adresse de la prochaine instruction à exécuter.

• RI : Registre d’instruction

• GPR : Ce sont des registres de travail, (general propose register) ils permettent de sauvegarder les résultats intermédiaires de calcul.

• ACC : Accumulateur. La majorité des instructions d’un CPU qui possède un accumulateur s’exécutent soit sur l’accumulateur seul soit entre l’accumulateur et un deuxième opérande. Le résultat de l’opération est stocké sur l’accumulateur. Certain CPU possèdent plusieurs accumulateurs.

• XR : Registre d’index. Ce registre peut être utilisé comme un registre GPR. En plus on dispose d’instructions permettant de l’incrémenter ou de le décrémenter. En plus il a une fonction spéciale qui d’une grande utilité dans la manipulation des tableaux de données. Il est en effet utilisé comme paramètre pour calculer les adresse suivant une forme particulière d’adressage appelée adressage indexé.

• RE : Registre d’état appelé aussi registre de condition. Il est formé de plusieurs bits appelés drapeaux qui sont positionné par l’ALU après chaque opération. On dispose d’un jeux d’instruction conditionnées par l’état de différents drapeaux. Par exemple le bit indicateur Z indique quand il est positionné que le résultat de l’opération est égal à Zéro. Le bit C indique que l’opération éxécutée à produit une retenue. Lz bit O indique un dépassement de capacité dans l’ACC est que le résultat est faux. Le bit N indique que le résultat est négatif . . .

• SP : pointeur de pile (Stack Pointer). Ce registre pointe (contient l’adresse) sur une zone mémoire qu’on appelle pile (LIFO) dans laquelle le processeur (ou le programmeur) peut sauvegarder momentanément des données sans être obliger de gérer le problème d’adressage.

• accumulateur

LE DEROULEMENT D’UNE INSTRUCTION

Le déroulement d’une instruction se fait en Horloge deux cycles, un cycle de recherche (fetch

cycle) et un cycle d’exécution.

Pendant le cycle de recherche, l’instruction Cycle Cycle

Recherche Exécution est chargée de la mémoire vers le registre d’instruction RI Cycle Instruction

Pendant le cycle d’exécution,

• L’instruction est analysée par le décodeur

pour déterminer la nature de l’opération ainsi que le nombre et le type des opérandes.

• Ces informations sont communiquées au séquenceur qui charge les opérandes dans les registres approprié et envoi à l’ALU les signaux de commandes lui indiquant l’opération à effectuer.

• L’ALU exécute l’opération et positionne les indicateurs du registre d’état

Le temps d’exécution d’une instruction dépend du type de l’opération à exécuter. Un cycle d’instruction peut s’étendre sur plusieurs cycles machines ou périodes d’horloge. Le terme cycle CPU est utilisé pour indiquer le temps d’exécution de l’instruction la plus courte.

STRUCTURE D’UNE INSTRUCTION

Les ordinateurs sont capables de faire un certain nombre d’opérations simple, par exemple additionner deux nombres, tester le signe d’une valeur numérique, copier le contenu d’un registre dans un autre, stocker le contenu d’un registre dans une accumulate registre mémoire ou charger le contenu d’une mémoire dans un registre.

Une instruction machine doit donc contenir un code opération et un ensemble d’adresses. Si on exclut les opérations entre AL registres, une instruction ressemblerait à CO ad1 ad2 ad3 :

CO : Code Opération

Ad1 et ad2 : adresses des opérandes

Ad3 : adresse ou doit être estoqué le résultat

Pour simplifier les programmes, les concepteurs de microprocesseurs ont opté pour une architecture avec des

instructions à une adresse. Ceci est rendu possible par l’utilisation d’un registre spécial appelé accumulateur. Les opérations se font entre l’accumulateur et un autre opérande dont l’adresse est précisée. Le résultat de l’opération est stocké dans l’accumulateur. L’instruction sera donc constituée seulement de deux champs CO | AD . Mais comme les processeurs avec un seul accumulateur sont un peu limités, on multiplie le nombre d’accumulateurs mais on a de nouveau des instructions à 3 champs puisqu’il faut préciser l’accumulateur utilisé CO Ax AD

Pour une machine 8 bits, le code opération est un nombre de 8 bits (1 octet) qu’on représente le plus souvent en Hexadécimal (2 chiffres). Le champ adresse quant à lui, peut être constitué de plusieurs octets, cela dépend de la taille mémoire. On aura par exemple des instructions du genre 3A 24 5678 (tous les nombres sont en hexadécimal)

3A = 0011 1010 = code de l’Opération

24 = 0010 0100 = code de l’accumulateur utilisé

5678 = 0101 0110 0111 1000 = adresse du deuxième opérande

Pour faciliter la lecture des programmes par « l’homme », on associe une mnémonique à chaque code opération, des noms pour les registres et on adopte une sorte de grammaire pour l’écriture des instructions, obtient des instructions du genre :

ADD AX, [3456] additionner le contenu de l’accumulateur AX avec le contenu de la case mémoire d’adresse 3456 avec résultat dans l’accumulateur

ADD [1258],BX additionner le contenu de l’accumulateur BX avec le contenu de la case mémoire d’adresse 1258 avec résultat dans la case mémoire.

LES MEMOIRES

Une mémoire est un dispositif capable d’enregistrer, de conserver et de restituer des informations codées en binaire dans un ordinateur.

HIERARCHIE DES MEMOIRES PAR PERFORMANCE

Les mémoires d’un ordinateur se répartissent en plusieurs niveaux caractérisés par leur temps d’accès et leur capacité. La figure 3.1 illustre cette hiérarchie. Plus on s’éloigne du CPU, plus le temps d’accès aux mémoires augmente ainsi que leur capacité alors que le coût par bit diminue.

• Les éléments situés dans l’unité centrale sont les registres, ils sont très rapides et servent principalement au stockage des opérandes et des résultats intermédiaires.

• La mémoire cache est une mémoire rapide de faible capacité. La mémoire cache est le plus souvent intégrée au processeur pour qu’elle soit la plus rapide possible. On peut avoir une partie sur le processeur (On chip cache) et une partie hors du processeur.

• La mémoire centrale et l’organe principal de rangement des informations utilisées par le CPU. C’est une mémoire à semi-conducteurs, son temps d’accès est beaucoup plus grand que celui des registres et de la mémoire cache.

• Les mémoires de masse sont des mémoires périphériques de grande capacité et de coût relativement faible. Elles servent d’éléments de stockage permanent et utilisent pour cela des supports magnétiques (disques, bandes) et des support optiques (disques optiques).

LES MEMOIRES A SEMI-CONDUCTEURS

Il existe de nombreuses variétés de mémoire à semi-conducteurs. Cette diversité vient du fait que la mémoire idéale à grande capacité, consommant peu d’énergie, de vitesse élevée, gardant son information en cas de coupure d’alimentation, n’existe pas. Les différentes catégories de mémoire que nous rencontrerons sont des compromis sur quelques paramètres indispensables, nous allons les classer en fonction de leurs utilisations.

Mémoire vive ou RAM

La mémoire vive est une mémoire dans laquelle on peut écrire ou lire une information. En anglais on la désigne sous le sigle RAM (Random Access Memory), mémoire à accès aléatoire, cela signifie qu’après avoir lu ou écrit dans une position mémoire, on peut lire ou écrire dans une autre position quelconque. Ceci par opposition avec le s mémoire à accès séquentiel (série), dans lesquels après avoir lu ou écrit dans une position mémoire, la prochaine opération de lecture/écriture ne peut porter que sur la position mémoire immédiatement voisine. Remarquons que la nomenclature RWM (read write memory) aurait été plus appropriée.

Le contenu d’une mémoire vive s’efface quand la tension d’alimentation disparaît, d’où la qualification de mémoire volatile.

On distingue les RAMs statiques et les RAMs dynamiques :

– Le taux d’intégration des RAM statique est assez faible et leur prix de revient (au Mbits) reste relativement élevé, par contre, leur temps d’accès est faible. Elles sont utilisées dans

Structure et Technologie des Ordinateurs par A. OUMNAD 11

les mémoires caches (interne et externe)

– Le taux d’intégration des RAM dynamique est élevé et leur prix de revient (au Mbits) est plus faible mais leur temps d’accès est assez élevé. Elles sont utilisées dans la mémoire centrale.

Mémoire Morte ou ROM

L’utilisateur ne peut que lire le contenu de cette mémoire. Elle est inscrite par le constructeur au moment de la fabrication selon les spécifications du client. On utilise ce genre de mémoire quand l’information qu’on y enregistre est une information figée qui n’est pas susceptible de subir un changement, comme par exemple les valeurs de la fonction sinus pour les angles compris entre 0 et 90°. S’il arrive malgré tout qu’on soit obligé de changer le contenu, il faut commander un autre boîtier au constructeur, ce qui demande beaucoup de temps (plusieurs semaines).

L’utilisation des ROM ne devient intéressante que si le nombre de boîtiers identiques est grand (plusieurs milliers), compte tenu du coût de développement initial (masque du contenu de la mémoire). Le gros avantage des mémoires ROM est de conserver leur contenu après une coupure d’alimentation, elle fait partie des mémoires non volatiles.

Mémoire morte programmable ou PROM

Lorsque l’information que l’on désire enregistrer dans une mémoire non volatile est susceptible de varier de temps en temps (comme un programme qu’on met au point par exemple), l’utilisation des ROM ne convient plus. On utilise alors des mémoires PROM programmable par l’utilisateur au moyen d’un dispositif adéquat appelé programmateur de PROM. Si après inscription et utilisation, le contenu s’avère inexact, on jette le boîtier et on en reprogramme un autre. L’opération prend quelques minutes.

Comme les mémoires ROM, le contenu des PROM ne s’efface pas après coupure d’alimentation.

Mémoire morte reprogrammable ou EPROM

Avec les PROM, pour changer le contenu, il faut jeter le boîtier est reprogrammer un nouveau. Cela peut devenir gênant du point de vue financier si les modifications deviennent trop fréquentes. Les mémoires EPROM (Electrically Programmable Read Only Memory) appelées aussi ROM effaçables, constitue une solution à ce problème. Quand on veut changer le contenu d’un boîtier, on n’est pas obligé de le jeter, on peut effacer son contenu en l’exposant aux rayons ultraviolets à travers une fenêtre de quartz placée sur le boîtier, puis enregistrer électriquement les nouvelles informations en appliquant des tensions plus élevées que la tension d’alimentation normale. L’effacement par ultraviolets dure une vingtaine de minutes. Comme pour les mémoires ROM, l’intégrité de l’information est conservée après disparition de l’alimentation.

Mémoire morte efaçable électriquement ou EEPROM

Ces mémoire non volatiles présentent l’avantage d’être inscriptible électriquement et effaçable électriquement d’où leur nom EEPROM (Electrically erasable programmable Read Only Memory) . Cela permet de gagner du temps car l’effacement électrique prend beaucoup mois de temps que l’effacement par ultraviolets.

Mémoire FLASH

Les mémoires flash sont des EEPROM à accès rapide. L’accès en lecture est comparable à celui des RAMs (<= 100 ns). L’accès en écriture est plus long ( <= 10 µs). On distingue des variantes à accès parallèle et d’autres à accès série. Sur les ordinateurs, elles sont utilisées surtout pour le stockage du bios. Ailleurs, ces mémoires sont utilisées dans beaucoup d’applications et sont promues à un avenir très prometteur. Les cartes à puces en sont fournies et elles remplacent déjà les Disques durs sur certains ordinateurs portables.

TECHNOLOGIES DES MEMOIRES

L’unité de base de stockage et la cellule qui permet de stocker un bit. Sa structure dépend du type de mémoire. Le regroupement de 8 cellules donne une case mémoire qui peut stocker un octet.

Cellule statique d’une mémoire vive

Dans ce cas, l’information est stockée dans une bascule comme une bascule D par exemple. Comme on le sait une fois la sortie de la bascule est dans un état, elle y restera tant qu’en ne vient pas la changer en mettant le bit à enregistrer sur l’entrée D et en envoyant un coup d’horloge sur son entrée horloge. Les mémoires ainsi construites sont appelées les RAM Statiques (SRAM). Toutes les bascules (D, R-S, J-K) avec ou sans horloge peuvent servir de point de mémorisation, mais pour des raisons d’encombrement, on utilise des bascules bistables constituées de 6 transistors MOS ou de 2 transistors bipolaires. Les MOS sont plus utilisés du fait de leur facilité d’intégration et de leur faible consommation. Même cette solution reste trop encombrante ce qui fait qu’en général les RAM statiques n’ont pas une très grande capacité. la figure Erreur ! Source du renvoi introuvable. illustre le principe de fonctionnement d’une cellule SRAM.

I Introduction

I.1 Architecture fonctionnelle

I.2 Le processeur

I.3 La mémoire centrale

I.4 Le Disque dur

I.5 Les disquettes et les CD-ROM

I.6 Le clavier la souris et l’écran

I.7 Le Bus

I.8 Les Unités d’entrés sorties (E/S)

I.9 BIOS et Système d’exploitation

I.10 Architecture matérielle

II Architecture du processeur

II.1 L’unité de contrôle

II.2 L’unité arithmétique et logique

II.3 Les registres

II.4 Le déroulement d’une instruction

II.5 Structure d’une instruction

III Les mémoires

III.1 Hiérarchie des mémoires par performance

III.2 Les mémoires à semi-conducteurs

III.3 Technologies des mémoires

III.4 Organisation par mot

III.5 Cycle de lecture

III.6 Mémoires magnétiques

III.6.1 Les disquettes

III.6.2 Les disques durs

III.7 Les interfaces de gestion de disques durs

III.7.1 Interface IDE (et ses variantes)

III.7.2 Interface SCSI

III.8 Les Mémoire Optiques

IV La mémoire cache

IV.1.1 Gestion des remplacements

V Les Bus

V.1 Bus Synchrone

V.2 Bus Asynchrone

V.3 LES BUS D’extension du PC

VI Représentation de L’information

VI.1 Représentation des caractères

VI.2 Représentation des nombres Entiers

VI.3 Représentation des nombres Réels

VII Les entrées Sorties

VII.1 Les techniques De gestion

VII.1.1 La scrutation

VII.1.2 Les Interruptions

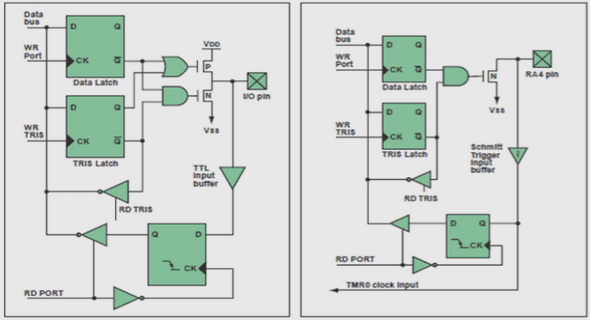

VII.2 Entrées/Sorties parallèles

VII.3 Entrées/Sorties série

VII.4 Interfaçage analogique

VII.4.1 L’échantillonnage

VII.4.2 Codage ou Quantification

VIII Retour sur Quelque aspects fondamentaux

VIII.1 Le chipset

VIII.2 Le contrôleur DMA

VIII.3 La gestion des interruptions

VIII.4 La mémoire virtuelle

VIII.4.1 La pagination (swapping)

VIII.4.2 Mécanisme de remplacement