RF and millimeter-wave switches

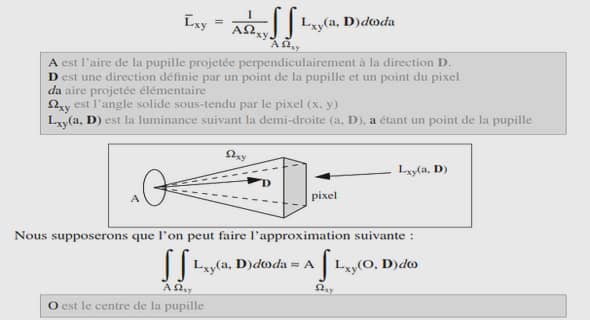

Radio Frequency (RF) switches are a critical building block in many communication systems. These devices can be used in a wide variety of fields, including aerospace, defense, automotive, military, networking & wireless infrastructure. RF switches are especially important in handheld devices (cell phones, tablets, etc.), and an example of their implementation within the RF front-end module is shown in Figure 1.1. There are three main types of RF switches, namely: SPST (Single-Pole Single-Throw), SPDT (Single-Pole Double-Throw), and MPMT (Multiple-Pole Multiple-Throw), the classification being based on the number of inputs and the number of outputs of the particular switch architecture under consideration. Figure 1.1 RF Switches in Frond-End Module Various millimeter-wave switches have been designed and reported with good performances on different processes. As an example, reference may be made to a 60GHz switch design using GaAs pHEMT technology and with low insertion loss and high isolation (Lin et al., 2004). In the same 60GHz frequency band, the asymmetric switch has been demonstrated to have an insertion loss and isolation of 1.9dB and 39 dB, respectively (Byeon & Park, 2013).

However, SOI is the technology of preference for most designers to achieve low cost, excellent performance, and low power designs. Examples of such SOI switches include the low insertion loss SPDT switch operating from DC to 60GHz shown in (Parlak & Buckwalter, 2011) and the 1W, 0.9dB insertion loss, millimeter-wave switch shown in (C. Li, Freeman, et al., 2017). In this thesis, the implementation of millimeter-wave switches working in 28GHz with low insertion loss, high isolation, and linearity is demonstrated. The proposed switches are designed in CMOS SOI 45nm technology from GlobalFoundries. Chapter 2 focuses on the physical structure of the SOI technology process and its benefits. Then, chapter 3 presents the switch parameters, the associated design procedure, as well as some techniques aimed at improving the performance of the switch. Chapter 4 describes the switch designs carried out during this research work, including results from rigorous post-layout simulations. In chapter 5, results from on-wafer measurements of the switches are presented. The final section summarizes the work presented in this thesis and puts forth some conclusions.

Benefits of GlobalFoundries 45RFSOI process for RF Switches The GlobalFoundries 45RFSOI has been demonstrated to offer excellent performance for FEMs (Front-End-Modules), including for the design of LNA, PA, and Switches at high frequencies (μWave and mm-Wave). To evaluate the high-frequency performance of RF transistors, fT and fMAX are used as key indexes that are used. The term fT refers to the frequency when the current gain of the device drops to unity under AC shorted output conditions. The term fMAX refers to the frequency when the power gain of the device drops to unity under conjugate matched input and output conditions. For the GlobalFoundries 45RFSOI process, reference may be made to (A.Rabbeni, 2017), which shows that the fT and fMAX for the transistor in this process (using a device with L=40nm, W=20μm) are among the best in their category for comparable technologies. Performances for various biasing conditions are shown in Fig 2.3.

In the 45RFSOI process, Global Foundries introduced significant performance improvements through the high-resistivity trap-rich substrate. (Tinella, Fournier, Belot, & Knopik, 2003) demonstrated the advantages of using high-resistivity (HR) substrate to reduce the losses in the RF switch design. However, (Lederer, Lobet, & Raskin, 2004) indicated that the HR SOI is still affected by the parasitic surface conduction, which degrades the effective resistivity and increases the substrate losses. These losses may be traced to the high fixed charges within the oxide layer attracting free carriers near the substrate interface. The trap rich layer was introduced between the interface of the BOX layer and the HR Si substrate to capture the free carriers near the substrate interface, resulting in improved effective resistivity and linearity( (Ali, Neve, Gharsallah, & Raskin, 2011), (Neve & Raskin, 2012) and (Yu et al., 2017)). It is worthwhile to note that GlobalFoundries provides two types of RF FETs in the 45RFSOI process: Thin-Oxide FET and Thick-Oxide FETs, with different values of device length. Thick-Oxide FETs with longer device lengths help to increase the breakdown voltage. Such a breakdown may occur due to a variety of reasons such as punch-through breakdown, gateoxide breakdown, etc. as described in Section 2.2.3. A higher breakdown voltage means that designers can design the high-power RF switch with a smaller number of stacked FETs, as presented in Chapter 4 of this thesis.

Series-Shunt Structure

Figure 3.3 The Series-Shunt switch structure There are several topologies for RF Switches, as mentioned in (X. J. Li & Zhang, 2010). These include variations in the matching-network (He, Xiong, & Zhang, 2012), λ/4 transmission lines (Uzunkol & Rebeiz, 2010), traveling-wave (Chao, Wang, Su, & Chern, 2007), or Unbalanced Double Shunt/Matching Network (Byeon & Park, 2013). These topologies have been shown to exhibit good performances for RF switches at high frequencies. However, these designs all require λ/4 transmission lines, which are not a problem in terms of size for very high-frequency applications (higher than 40GHz). In this thesis, the switches are designed to operate at 28GHz; hence the topologies referenced earlier are not suitable, given that the chip area for RF switches is too limited, according to our integration requirements.

The Series-Shunt Topology is a good choice for RF Switch design in this work. Several designs with good performances have been described in the literature, such as (Lin et al., 2004), (C. Li, Freeman, et al., 2017), (C. Li et al., 2018), (Parlak & Buckwalter, 2011), etc. Coupled with the inherent benefits that stem from the SOI process, the Series-Shunt topology has several attractive advantages for RF Switches. Figure 3.3 shows the schematic of the switch structure using the Series-Shunt topology. The voltage logic control for the Series FETs is the inverse of the logic control for the Shunt FETs. It means that the shunt FETs are OFF while the series FETs are ON, and vice versa. Figure 3.4 The equivalent switch model in transmitting mode The small-signal equivalent circuit of the series-shunt topology is now analyzed in the ON (transmitting mode) and OFF (isolation mode) states. As shown in Figure 3.3, M1 refers to the series FETs, and M2 refers to the shunt FETs. Figure 3.4 is the equivalent circuit of the structure in Figure 3.3 when M1 is ON, and M2 is OFF. Under these conditions, the signal is allowed to be transmitted from port 1 to port 2 (or vice versa). The S-Parameter S21 in this mode is a measure of the insertion loss of the switch and identified using the ABCD matrix given by (3.2) below (Yu et al., 2017). By applying the conversion from the ABCD matrix to the S-Parameter matrix, the value of S21 is given by (3.3). Consequently, the value of the Insertion Loss (in dB) of the ON-state switch in Figure 3.4 is given by (3.4).

Asymmetric SPDT

The design procedure for an SPDT switch is similar to that of an SPST switch, and with similar performance compromises between insertion loss and isolation along a switching arm. In general, the SPMT (Single-Pole Multi-Throw) switch with T number of throws has more insertion loss in comparison with the SPST switch, the insertion loss becoming more as the number of throws T becomes higher. This is because when any single arm is ON, isolation through the T-1 OFF arms is optimized by reducing the value of their COFF, as seen in Figure 4.5 below. As shown earlier, sizing the transistors to reduce COFF leads to a larger RON, hence resulting in higher insertion loss. As a result, the dimensions of the SPDT switch have to be re-optimized compared to the original SPST switch. Figure 4.6 shows the schematic for the asymmetric SPDT switch. The gate voltages are set to +1V to turn ON the transistors or set to -1V to turn them OFF. As mentioned in (Byeon & Park, 2013), an asymmetric SPDT switch includes two arms with non-identical topologies. The TX arm for an asymmetric SPDT switch is designed with matching-network topology, resulting in a low insertion loss but also low isolation (Uzunkol & Rebeiz, 2010). On the other hand, the RX arm for an asymmetric SPDT switch is an SPST switch with a traveling-wave topology (including a transmission line) that has high isolation and, consequently, a higher insertion loss (Schindler & Morris, 1987). After comparison, it was determined that for the design in this research, both the TX and the RX arms of the asymmetric SPDT would use the same series-shunt structure without transmission line, as presented earlier. The primary motivation behind the series-shunt structure is that it helps to reduce the overall switch dimensions size, and hence affords better integration in FEM architecture. Of course, the performance specifications for a required application ultimately drive the choice of switch topology to be used.

INTRODUCTION |