Vers l’intégration de condensateurs à trois dimensions

Le chapitre précédent a traité des mécanismes physiques associés au vieillissement de condensateurs ferroélectriques élémentaires. Plus particulièrement, des études “amont” ont été menées, en collaboration étroite avec l’IMEC, sur des condensateurs à base de SBT destinés à être intégrés dans une architecture silicium submicronique (projet FLEUR). Les différentes caractérisations ont montré que, bien que présentant une bonne endurance, les condensateurs Pt/SBT/Pt ne possèdent pas une polarisation rémanente très importante. Ainsi, afin de permettre l’intégration du matériau SBT dans une architecture FeRAM associée à des technologies ≤ 0,18 µm, il est apparu nécessaire de développer des condensateurs intégrés présentant une géométrie à trois dimensions (3D). L’intégration et l’optimisation de réseaux de condensateurs “tests” sont effectuées à l’IMEC en partenariat avec STMicroelectronics (Catane-Italie). C’est dans ce cadre que la collaboration entre l’IMEC et le L2MP a été étendue à l’étude comparée, par des mesures électriques et des analyses microstructurales, de réseaux de condensateurs à deux et à trois dimensions. Il a ainsi été possible d’effectuer des premières études sur l’impact de la géométrie du condensateur sur sa réponse électrique. Un accent particulier a été mis sur la caractérisation de l’apport des bords du condensateur ferroélectrique (encore appelés “side walls”) dans la réponse électrique des condensateurs à trois transmission) et à l’échelle du réseau de condensateurs (diffraction des rayons X sur source synchrotron). L’ensemble de ces études a permis de proposer un modèle électrique et microstructural du condensateur 3D. Jusqu’à présent, seuls quelques groupes industriels (ST Microelectronics, Infineon, Fujitsu, Symetrix…) ont engagé une politique de recherche et développement axée sur la géométrie 3D. Compte tenu du caractère “novateur et confidentiel” de ces recherches, peu de travaux ont été publiés. De ce fait, il a été difficile de comparer les résultats obtenus à ceux de la littérature.

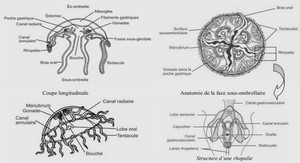

Comme cela a été précisé dans le paragraphe 1.1.2.6, les études publiées jusqu’à présent portent sur trois grands types de géométrie 3D : les condensateurs pseudo-3D empilés (Johnson et al., 2003 ), la technologie en “trous” (“trench approach”) (Joshi, 2004) et la technologie 3D verticale (Nagel et al. 2004). Dans le cadre du projet FLEUR, le choix technologique a été orienté vers les condensateurs pseudo 3D qui présentent la géométrie particulière indiquée sur la Figure 3-1. L’empilement des couches formant l’électrode inférieure du condensateur est de même nature que celui des condensateurs élémentaires (section 2.1.1.2). Toutefois, cette électrode Pt/IrO2/Ir/Ti(Al)N est gravée à intervalles réguliers afin de définir des motifs périodiques sur le wafer (Lisoni et al., 2004). Le film mince de SBT est ensuite déposé, sur cet arrangement périodique, par MOCVD dans des conditions équivalentes à celles utilisées pour les “short loops” (400 – 440 °C). Ainsi, le film mince de SBT (~120 nm d’épaisseur) présente des “modulations” relatives à la gravure de l’électrode inférieure (Figure 3-1-b présente une électrode supérieure de platine qui recouvre entièrement le film mince de SBT déposé sur l’électrode inférieure. Il s’agit là d’un condensateur 3D puisque la partie du film ferroélectrique déposée sur les bords du condensateur contribue à la réponse électrique. Par opposition, un condensateur 2D, possède une électrode supérieure plus petite que l’électrode inférieure. Dans ce cas, la partie du film ferroélectrique déposée sur les bords de l’électrode inférieure ne contribue pas à la réponse électrique.

Pour terminer, deux remarques supplémentaires peuvent être faites sur la géométrie 3D. La Figure 3-1-a montre que l’électrode inférieure est déposée directement sur un plug de tungstène assurant le contact électrique. D’autre part, ces images montrent aussi que les condensateurs sont encapsulés par différentes couches de protection dont l’une d’elle a une composition de type SrTaOx. Cette remarque aura son importance lors de la caractérisation chimique des réseaux de condensateurs, le strontium et le tantale contribuant à la fois dans la couche d’encapsulation et dans SBT. 3-2 comportent seulement 3 condensateurs alors qu’en réalité les réseaux étudiés comprenaient 10 ou 50 condensateurs. Dans la direction longitudinale, ces réseaux s’étendaient sous la forme de bandes (“stripes”) de 100 ou 200 µm de long. Les études ont porté sur cinq types de réseaux de condensateurs : condensateurs 3D avec ou sans gravure de SBT, condensateurs 2D avec ou sans gravure de SBT et “pseudo- condensateurs” de SBT gravés déposés sur SiO2/Si. Comme l’indique la Figure 2D non gravés). Toutefois, il faut noter que l’étape de gravure est identique quel que soit le réseau et qu’elle réduit la portion de SBT déposée entre les électrodes inférieures sur une distance de 0,8 µm. D’autre part, c’est uniquement dans le but de caractériser d’éventuelles variations microstructurales liées à la nature du substrat que le réseau de “pseudo- condensateurs” gravés sur SiO2/Si a été étudié. En effet, ce dernier ne possédant pas d’électrode, il n’est pas possible d’effectuer des mesures électriques.