Systèmes d’interconnexion dans un SoC

Variété des systèmes d’interconnexion

Il existe différents types de systèmes d’interconnexion utilisables dans un SoC dont le point-`a-point, le bus partagé ou hiérarchique, le crossbar et le réseau sur puce [106]. Figure 3.1: Systèmes d’interconnexion point-`a-point L’approche point-`a-point (figure 3.1) est la solution la plus directe et la plus simple. Il s’agit de celle qui est utilisée pour concevoir les architectures cˆablées évoqués au chapitre précédent. Elle consiste `a connecter les différents unités de calcul d’un système avec des fils dédiés et exclusifs pour les échanges de données. Par conséquent, cette approche est efficace pour des systèmes `a bande passante élevée ce qui est le cas dans le domaine de la vision. Elle offre une très grande possibilité de parallélisation mais implique une faible réutilisation des unités de calcul du fait de la rigidité des connexions. Il en résulte une très faible flexibilité de communication entre les unités de calcul. Cette solution reste cependant convenable pour des systèmes `a faible nombre d’unités. Ainsi, faire évoluer un système avec cette approche, nécessite de complexifier les connexions, en rajoutant de fa¸con croissante des liaisons entre les unités. Cette méthode devient, de manière évidente, difficilement gérable avec une démarche d’intégration croissante des unités de calcul pour des raisons de dépendances physiques entre les liaisons et de synchronisation entre les signaux. L’approche par bus partagé (figure 3.2(a)) est une technique très utilisée pour interconnecter des unités de calcul. Cette approche convient également pour des systèmes `a faible nombre d’unités de calcul. Par exemple, nous pouvons citer le bus standard ARM AMBA [107] qui est très répandu dans les SoCs. Différents bus sont généralement connectés sous forme hiérarchique (figure 3.2(b)) en regroupant des unités selon les contraintes Figure 3.2: Système d’interconnexion de type Bus en bande passante. Un bus est généralement composé de lignes de données, de lignes de contrˆole et d’un arbitre. Ce type d’approche présente l’avantage d’avoir une mise en oeuvre simple `a faible coˆut mais est cependant très limité en terme de performance car ce type de communication ne permet de faire communiquer qu’un seul module `a la fois selon l’arbitrage. Il en résulte des formations de goulot d’étranglement de donnée très fréquents avec l’augmentation des unités connectés. Un approche coˆuteuse consiste `a utiliser un crossbar pour interconnecter les unités de calcul. Le principe consiste `a définir une matrice de multiplexeurs permettant `a toute unité du système de communiquer avec une autre, de fa¸con la plus performante possible de manière point `a point, et en autorisant ainsi des communications en parallèle. Cette approche est très coˆuteuse en surface mais convient pour des systèmes avec un nombre d’unités de calcul réduit. Un compromis consiste également `a réaliser partiellement cette matrice en fonction des besoins de communication si ils sont prévisibles. En exemple, nous pouvons citer l’architecture du processeur reconfigurable, appelé Reconfigurable Operators for Multimedia Applications (ROMA) [108], proposé récemment par le CEALIST. Cette architecture utilise un crossbar comme système d’interconnexion entre des unités de calcul `a grains épais et différents bancs mémoires. Pour un SoC dédié `a la vision, tous les types d’interconnexion présentés dans cette section sont utiles selon le profil et la finalité du système. Généralement, différents types d’interconnexion sont combinés dans un mˆeme SoC, en utilisant les avantages de chacun. Les communications point-`a-point sont par exemple réservées pour les parties critiques en terme de temps et les communications par bus partagé sont plutˆot dédiées pour des périphériques lents et peu demandeurs en bande passante. L’utilisation de crossbar incomplet permet de résoudre partiellement les exigences en performances pour des SoCs actuels dédiés `a la vision. Cependant, ces solutions se révèlent très rapidement limités en nombre d’unités de calcul. Avec des technologies d’intégration croissantes, il est a présent envisageable d’implémenter dans un SoC des systèmes d’interconnexion plus avancés comme un réseau sur une seule puce.

Réseaux sur puce

Définition

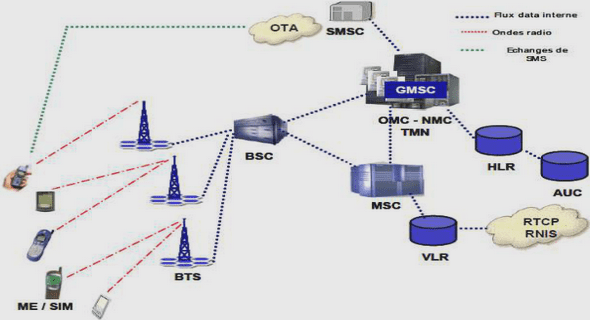

Depuis une dizaine d’années [12, 13], les premiers concepts et prototypes de réseau de communication sur puce, appelé Network-on-Chip (NoC), sont apparus. Selon la définition proposée par Dally [14], un réseau d’interconnexion correspond `a un système permettant de transporter des données entre des terminaux. La figure 3.3 illustre un exemple avec trois terminaux T0, T1 et T2. T0 T1 T2 Figure 3.3: Réseau d’interconnexion du point de vue fonctionnel avec trois terminaux Les terminaux se communiquent en se transmettant des messages (données) au travers du réseau. Dans notre cas, un terminal correpond `a un point source ou un point de chute (sink) des données. Le réseau peut effectuer plusieurs connexions simultanées entre les terminaux autorisant ainsi plusieurs communications en parallèle et les modifier `a tout instant. Un réseau est défini comme un système car il est composé de différentes ressources : mémoire, canal de communication et d’un élément de commutation de données appelé routeur qui s’organisent pour transmettre les messages entre les terminaux. Nous Chapitre 3. Systèmes d’interconnexion dans un SoC 74 définissons un canal comme un ensemble de fils interconnectant les ports d’entrée et de sortie des routeurs permettant de transporter les données. A l’échelle du SoC, considérons `a présent que chaque terminal correspond `a une unité de calcul. L’approche par réseau d’interconnexion, illustrée par la figure 3.4, consiste `a paquetiser les messages pour les transporter d’une unité source vers une unité destination, `a travers un réseau de routeurs reliés par des canaux physiques de communication. PE0 PE1 PE2 PE3 routeur Figure 3.4: Système d’interconnexion de type réseau

Structure d’un message

Chaque message, illustré par la figure 3.5, est fractionné en plusieurs paquets de données [14]. Le paquet est l’unité d’information du réseau de communication. Ils sont en général composés d’un en-tˆete (header ) contenant des informations de contrˆole et de la donnée utile `a transporter. Afin de pouvoir ˆetre transmis dans le réseau, ces paquets sont divisés en paquets élémentaires appelés flits (contraction de flow control digits). Ces flits peuvent ˆetre encore subdivisés en phits (contraction de physical units) correspondant `a une unité de donnée qui peut ˆetre transférée physiquement `a travers un canal de données entre deux routeurs en un cycle d’horloge. Les performances (i.e. latence, bande passante, consommation) d’un réseau sur puce dépendent dans un premier temps du choix de la granularité de chaque unité de données (message, flits, phits). message paquet flit phit Figure 3.5: Structure d’un message dans un réseau NoC [14] Chapitre 3. Systèmes d’interconnexion dans un SoC 75 De nombreuses études ont été effectuées depuis une dizaine d’années, pour porter et évaluer différentes solutions d’interconnexion de systèmes multi-processeurs vers cette nouvelle approche de réseau de communication. C’est le cas par exemple pour l’architecture Chameleon dont les communications ont été évaluées dans un contexte de réseau de processeurs sur puce [15]. La spécification d’un réseau se base sur trois points essentiels : la topologie du réseau qui précise la structure du réseau, la technique d’aiguillage qui spécifie les mécanismes d’accès aux ressources et l’algorithme de routage qui détermine la gestion du trafic (distributivité des données) dans le réseau. Ces points sont inter-dépendants. Par exemple, le choix d’une topologie implique un choix d’algorithmes de routage propres `a la topologie. Ainsi, toute la difficulté du concepteur consiste `a réaliser des compromis en terme de consommation, performance, robustesse et complexité.