Etude des structures à nano-cristaux de silicium

Au cours de ces dix dernières années, les nano-cristaux de silicium ont été introduits dans les mémoires Flash afin d’améliorer leurs performances : réduction de dimensions, robustesse par rapport aux défauts de l’oxyde, basse consommation en puissance, bas coût de fabrication, etc… L’objectif de ce chapitre est de présenter une modélisation du comportement électrique des mémoires à nodules de silicium lors de leur écriture en fonction des paramètres des dots. Dans un premier temps, nous avons étudié l’effet de la répartition non uniforme de la charge stockée sur les caractéristiques électriques de ces dispositifs, puis nous avons développé un modèle pseudo 2D de l’opération d’écriture de la mémoire par porteurs chauds. La dernière partie de ce chapitre est consacrée à la caractérisation électrique de structures à nodules fabriquées par la société STMicroelectronics Catagne dans le cadre du projet européen ADAMANT (Advanced Memories based on Discrete Traps). Les nodules considérés dans notre étude sont des nano-cristaux de silicium séparés les uns des autres par du SiO2. Ils remplacent la grille flottante conventionnelle des mémoires Flash et sont constitués de demi-sphères en silicium offrant leur section la plus large à l’injection tunnel (cf. Fig. (IV.1)).

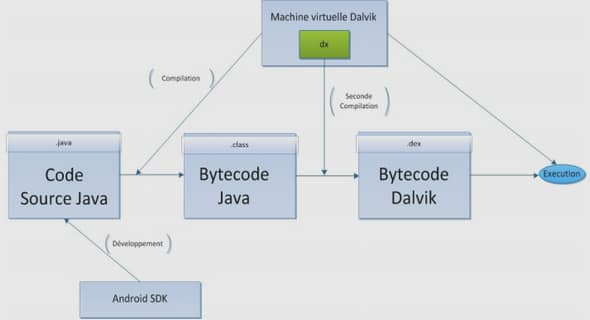

l’information lors d’une détérioration locale de l’oxyde. De surcroît, ces nodules sont supposés uniformément répartis dans l’oxyde du transistor entre l’oxyde tunnel d’épaisseur (tox1) et l’oxyde de contrôle d’épaisseur (tox2). Comme le montre la figure (IV.1), seule une faible portion Reff de la surface totale de l’oxyde de grille est occupée par les nano-cristaux de silicium. Ce coefficient Reff est proportionnel à la densité (Ndot) et au diamètre (Ddot) des nodules : Comme nous l’avons rappelé dans le chapitre I, l’opération d’écriture des mémoires Flash à nodules consiste à stocker des électrons dans les nano-cristaux, soit par le biais du mécanisme Fowler–Nordheim (FN), IFN, qui est assez lent (de l’ordre de la micro- seconde) et uniforme (cf. Fig. (IV.2.a)), soit par le mécanisme de porteurs chauds (CHE) [Tam’84], qui est plus rapide (facteur 10) mais plus coûteux en terme d’énergie car le transistor doit être polarisé en régime de saturation (VDS fort) pour créer des paires électrons-trous (par ionisation par impact). Toutefois, l’écriture par porteurs chauds permet un accès sélectif à un seul point mémoire (cf. Fig. (IV.2.b)) puisque la création de paires électrons-trous est localisée dans une zone proche du drain ou de la source suivant la polarisation (VD-VS) appliquée [Eitan‘00]-[Lusky’01]. Les trous ainsi générés se dirigent vers le substrat, tandis que les électrons suivent différents chemins : sous l’influence du champ électrique entre l’interface et la grille, une partie des électrons traverse l’isolant de grille du transistor pour atteindre soit la grille, soit les nodules (qu’ils chargent) ; la majeure partie des électrons générés par ionisation rejoignent le drain (ou la source suivant leur point de départ), sous l’influence du champ électrique entre les extrémités du canal.

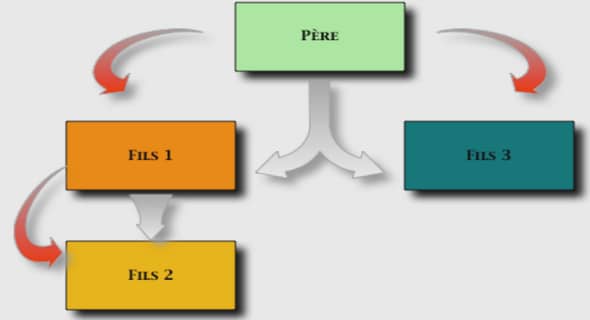

Par exemple, la figure (IV.2.c) présente une schématisation de la non uniformité de charges qui découlerait de charges stockées uniquement à l’intérieur de quelques nodules proches du drain. Cette possibilité de chargement discret, localisé près d’une jonction (drain et/ou source) offre la possibilité d’une logique 2 bits pour les mémoires à nodules [Bloom’01], c’est à dire quatre états possibles : Comme nous l’avons rappelé au chapitre III, les modélisations de type Pao et Sah et en feuillet ne prennent pas en compte ce type de non uniformité dans le développement de l’expression du courant de drain. Le modèle segmenté, développé lors de nos travaux sur les non uniformités des transistors (voir chapitre III), permet de surmonter cette difficulté. Par conséquent, pour simuler le courant de drain des transistors ayant les profils de charges reportés sur la figure (IV.3.a), nous avons adapté le modèle segmenté en considérant la structure comme équivalente à la juxtaposition de N transistors (de longueur L/N) ayant chacun une charge fixe constante dans l’oxyde mais pouvant être différente d’un segment à l’autre. Le courant de drain des N transistors élémentaires est évalué à l’aide du modèle en feuillet [Brews’78]. A des tensions de grille (VGS) et de drain (VDS) fixées, le potentiel de surface (et par conséquent l’écart entre les quasi-niveaux de Fermi, ΦC), est calculé pour chaque transistor en supposant un flux de courant conservatif le long du canal. Le système de N équations à N−1 inconnues peut alors être résolu par la méthode du pont diviseur. Cependant, comme nous l’avons déjà signalé, l’utilisation du pont diviseur n’est valide que si la somme de tous les courants tunnels est négligeable par rapport au courant de drain IDS. Pour les structures considérées, ces conditions sont respectées puisque le courant d’injection est très petit devant IDS et que les fuites de grille sont considérées comme négligeables.