La capacit´e d’int´egration des syst`emes sur puce augmente, cette croissance suit encore la loi de Moore [3]. Le principe de Dennard [4] mentionne qu’`a chaque miniaturisation la densit´e de puissance est constante. Cela revient `a dire que si la taille d’un transistor est divis´ee par 2, sa consommation est r´eduite par 4. Cependant, en r´eduisant la taille des transistors, il n’est plus possible de r´eduire la tension et le courant dont ont besoin les transistors pour fonctionner de mani`ere fiable. Cela annonce ainsi la fin de l’`ere Dennard. La consommation est devenue l’une des raisons principales de la limitation en performance. La performance des syst`emes int´egr´es a tendance `a stagner. La r´eduction de la consommation n’est plus possible car la consommation statique augmente. Cette augmentation de la consommation statique modifie particuli`erement le rapport entre la consommation statique et dynamique. La consommation affecte la temp´erature du circuit int´egr´e qui, par effet boule de neige, augmente la consommation statique qui d´epend de la temp´erature.

Des techniques de gestion sont ´etudi´ees `a diff´erents niveaux afin de r´eduire la consommation totale des syst`emes. En effet, la gestion de la consommation des circuits peut ˆetre r´ealis´ee au niveau syst`eme d’exploitation, au niveau compilateur, au niveau circuit et syst`eme et voire mˆeme au niveau technologique.

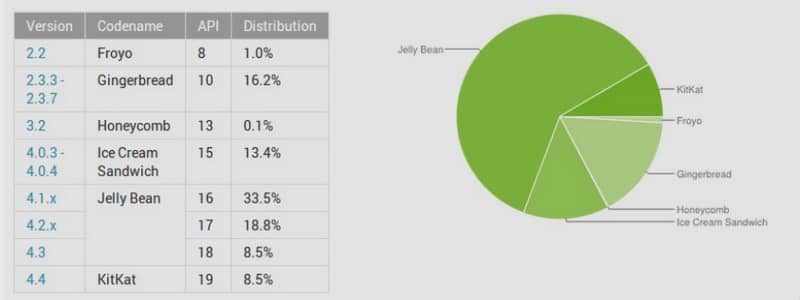

Il existe d’innombrables techniques au niveau logiciel. Nous allons ´evoquer quelques exemples. La gestion au niveau syst`eme d’exploitation peut ˆetre r´ealisee en d´eterminant la quantit´e de travail pour ex´ecuter une tˆache. Par la suite le syst`eme d’exploitation d´ecide de la fr´equence `a appliquer afin d’ex´ecuter la tˆache (principe de la technique du DFS) [5]. La gestion de la consommation au niveau architecture et logiciel peut ˆetre r´ealis´ee en combinant des cœurs heterog`enes. Par exemple, l’architecture big.LITTLE [6] de ARM est une architecture h´et´erog`ene combinant deux clusters, un avec des cœurs basse consommation (Cortex-A7) et l’autre avec des cœurs haute performance (Cortex A15). Chaque cluster poss`ede sa propre gestion de la consommation-performance, bas´ee sur la technique DVFS. Selon la performance requise par une tˆache, elle peut ˆetre migr´ee d’un cœur `a un autre cœur afin de r´eduire la consommation. La migration de tˆache permet soit d’am´eliorer l’exp´erience de l’utilisateur soit de respecter la performance de la tˆache, i.e. que la tˆache soit finie `a temps.

Technologie CMOS BULK

Au fil des ann´ees, les transistors MOSFET (Metal Oxide Semiconductor FieldEffect Transistor) de type N ou P ont beaucoup ´evolu´e. Ces transistors sont utilis´es pour former des portes logiques CMOS (Complementary Metal Oxide Semiconductor),

En CMOS BULK, la gestion du compromis consommation-performance peut etre realis´ee en modifiant la tension d’alimentation, la fr´equence ou la tension du substrat Vbb . La modification de la tension du substrat entraine un changement de la tension de seuil Vth des transistors. Vth est d´efinie comme etant la tension entre la grille et la source pour laquelle la zone d’inversion apparait ; un canal de conduction se cr´ee entre la source et le drain. Lorsque la tension grille-source est inferieure `a la tension de seuil, le transistor est bloqu´e ; il n’est pas conducteur. Sinon, le transistor est passant ; il conduit le courant entre la source et le drain. Vth peut ˆetre fix´ee `a la calibration pour compenser les variations de proc´ed´es de fabrication ou selon la technologie, la tension Vth peut ˆetre modifi´ee en cours d’execution afin d’agir sur la performance ou la consommation. Cependant, en CMOS BULK, il est n´ecessaire d’implanter des caissons profonds (triple-well) pour pouvoir modifier dynamiquement la tension de substrat. De plus, les transistors partagent le mˆeme caisson, si l’on souhaite appliquer une technique de Body Biasing, alors les transistors d’un mˆeme caisson sont polaris´es au mˆeme potentiel.

Une technique souvent utilis´ee au niveau conception post-routage est la technique Multi-Vth. L’objectif est de r´eduire la consommation statique des chemins o`u la vitesse n’est pas requise. Certaines cellules LVT (low Vth) sont remplac´ees par des cellules HVT (high Vth) afin d’augmenter la tension de seuil de ces chemins. Cependant, il est n´ecessaire de v´erifier l’int´egrit´e du signal, par exemple les retards de couplage.

De plus, la course `a la miniaturisation en technologie CMOS BULK, a atteint ses limites, physiques et ´economiques. En effet, le coˆut de d´eveloppement d’une technologie augmente par nœud technologique. Afin de satisfaire le march´e des syst`emes int´egr´es, des technologies ont ´et´e d´evelopp´ees afin de produire des circuits plus performants. Cela est dˆu au fait qu’ils embarquent plus de transistors pour une mˆeme surface. Le d´eveloppement de nouvelles technologies est donc un enjeu strat´egique pour le march´e du semi-conducteur. Actuellement deux choix technologiques se d´emarquent.

FinFET

La technologie FinFET (Fin-shaped Field Effect Transistor) a ´et´e d´evelopp´ee par INTEL. Il s’agit d’un transistor bas´e sur un transistor classique MOSFET dont la grille entoure le canal de tous les cˆot´es car le drain et la source forment une «ailette » (Fin en anglais) sur´elev´ee. Ce transistor est d´ecrit comme un transistor 3D ou tri-gate . Pour un mˆeme nœud technologique qu’en CMOS BULK, les transistors consomment moins `a performance identique. Cette r´eduction de la consommation r´esulte de la r´eduction des courants de fuite par le contrˆole electrostatique du canal qui a ´et´e am´elior´e [9]. De mˆeme, pour une mˆeme consommation qu’en CMOS BULK, la fr´equence appliqu´ee aux transistors en technologie FinFET peut ˆetre augment´ee. Cependant, cette technologie n´ecessite un investissement ´economique pour d´evelopper de nouvelles lignes de production et des techniques pour les concepteurs. De plus, le proc´ed´e de fabrication de cette technologie est tr`es complexe.

1 Introduction |