Les SoCs complexes hétérogènes et leur

sécurité

Les SoCs complexes hétérogènes

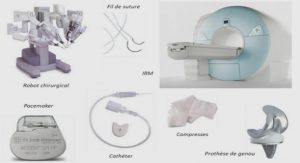

Un SoC complexe hétérogène est un ensemble de composants matériels et logiciels conçus et intégrés dans une seule puce électronique pour réaliser un ensemble de fonctionnalités. Typiquement, les SoCs complexes hétérogènes modernes intègrent (mais pas toujours) plusieurs processeurs de différentes natures(processeurs pour les opérations temps réel, processeurs pour les applications générales, …), plusieurs composants complexes et différents tels que des unités de calcul spécifiques programmables et/ou non programmables (DSP, ASICIP, FPGA), des composants de mémorisation variés, des périphériques E/S, et des réseaux de communication complexes (bus, NoC). La figure 2 présente deux architectures de SoC complexe hétérogène des deux leaders mondiaux du marché des circuits embarquant une matrice de FPGA et un système multicœurs, Xilinx et Intel. La figure 2-a présente le SoC Xilinx Zynq Ultrascale+ [31] et la figure 2-b présente le SoC Intel Stratix 10 SX [32]. Les deux SoCs intègrent des composants de technologie différente, quatre processeurs pour les applications générales (Cortex-A53), différents type de mémoires, une partie reconfigurable (FPGA UltraScale) et de nombreuses interfaces.Aujourd’hui, les SoCs complexes hétérogènes sont de plus en plus performants avec une réduction de la consommation d’énergie, du coût en surface de silicium. Leur partie reconfigurable (FPGA) constitue un support de développement pour une grande variété d’applications très diverses car il est possible d’implémenter n’importe quel circuit puis de configurer le réseau de portes logiques pour changer le fonctionnement de circuit. Elle permet également d’accélérer d’un facteur important le traitement des données par rapport à un logiciel exécuté par les processeurs [33]. Pour ces avantages, les SoCs complexes hétérogènes sont très répandus dans plusieurs domaines, on les trouve dans le domaine grand public (smartphone, console de jeux, appareil photos, …), dans le domaine des transports (système de navigation, conduite autonome, …), dans le domaine médical (imagerie, opération robotisée, …), dans le domaine des télécommunications (mobile, routeur, satellite, …), dans l’industrie (commande, capteurs intelligents, robot, …), etc.

Le bus à l’interface logiciel/matériel dans un SoC complexe hétérogène

Le bus à l’interface logiciel/matériel dans un SoC complexe hétérogène est un élément très important, il relie les divers composants du SoC, la mémoire, les processeurs, les périphériques E/S, …etc. Le bus relie les interfaces maîtres et esclaves des composants matériels du type IP (certaine IP peuvent avoir plusieurs interfaces à la fois, comme l’IP#2 dans la figure 3). Les interfaces maîtres sont responsables d’initialiser des requêtes d’écriture ou de lecture destinées à des interfaces esclaves qui ont seulement le droit d’exécuter les requêtes. Le bus utilise un système d’ID pour identifier l’émetteur et le récepteur d’une requête et un protocole d’arbitrage pour gérer les communications et résoudre les conflits d’accès.Un SoC complexe hétérogène peut contenir plusieurs types de bus qui peuvent être différents au niveau du protocole utilisé, la largeur du bus, le débit, l’utilisation des signaux de control, etc. Le passage d’un type à un autre nécessite des convertisseurs de protocoles et des FIFOs. Parmi les types de bus, on trouve le bus AXI (Advanced eXtensible Interface) qui a vu le jour dans la spécification du standard AMBA3 (Advanced Microcontroller Bus Architecture 3), il est utilisé par Xilinx et Intel pour connecter certaines des IP matérielles intégrées dans leurs SoC.C’est 5 canaux sont les suivants : Le canal d’adresse de lecture est utilisé par l’interface maître pour transmettre à l’interface esclave l’adresse à lire. Parmi les signaux utilisés dans ce canal, on trouve ARADDR[Largeur du bus d’adressage : 0], ARVALID, ARREADY, et ARPROT[2 : 0] qui sera détaillé dans la suite de ce chapitre. Le canal de lecture de donnée est utilisé par l’interface esclave pour transmettre la donnée enregistrée à l’adresse reçue par le canal d’adresse de lecture. Parmi les signaux utilisés dans ce canal, on trouve RDATA[Largeur du bus de donnée : 0], RVALID, RREADY, RRESP[1 : 0]. A la fin de la transaction, l’interface esclave envoie une réponse à l’aide des signaux RRESP[1 : 0] pour informer l’interface maître de l’échec ou le succès de la transaction. Le canal d’adresse d’écriture est utilisé par l’interface maître pour transmettre à l’interface esclave l’adresse à modifier. Parmi les signaux utilisés dans ce canal, on trouve AWADDR[Largeur du bus d’adressage : 0], AWVALID, AWREADY, BRESP[1 : 0], BVALID, BREADY et AWPROT[2 : 0] qui sera également détaillé dans la suite de ce chapitre. Le canal d’écriture de donnée est utilisé pour recevoir la donnée à enregistrer dans l’adresse envoyée par l’interface maître. Parmi les signaux utilisés dans ce canal, on trouve WDATA[Largeur du bus de donnée : 0], WVALID, WREADY Le canal d’écriture de réponse est utilisé pour informer l’interface maître de l’acceptation ou du rejet de la requête. Parmi les signaux utilisés dans ce canal, on trouve BRESP[1 : 0], BVALID et BREADY. Les signaux …VALID et …READY dans chaque canal sont des signaux de handshake utilisés par les deux interfaces, maître et esclave, pour indiquer à quel moment ils sont prêts à échanger des données. Les signaux BRESP[1 : 0] et RRESP[1 : 0] sont utilisés pour envoyer une réponse à la requête initiée par l’interface maître (échec ou succès). Si la transaction est correcte, l’interface esclave envoie un OK en envoyant la valeur binaire “00’’. Si la transaction échoue, l’interface esclave peut envoyer deux types d’erreur [34]: L’erreur DECERR (la valeur binaire “11”) qui est utilisée pour informer l’interface maître que le bus n’a pas réussi à accéder à l’interface esclave.