Le 25 Mars 1974, le français Roland Moreno dépose un brevet décrivant un circuit microélectronique embarquant une mémoire, intégrée dans une fine carte plastique. Ces circuits sont appelés cartes à puce, ou smartcard en anglais. Deux ans plus tard, dans le but de sécuriser les informations contenues dans cette mémoire, un autre français, Michel Ugon, parviendra à intégrer un microprocesseur dans ces cartes plastiques. Le microcontrôleur sécurisé est né. Depuis, la carte à puce s’est très largement répandue dans de nombreux domaines tels que la communication (carte SIM), le secteur bancaire (carte bancaire), le médical (carte vitale) ou comme moyen d’identification (passeport biométrique, badge d’entreprise…).

Composition et fonctionnement des cartes à puces

La communication entre une carte à puce et le lecteur est réalisée par un micromodule doré très mince, mettant en contant les broches du lecteur avec les différents contacts de la puce embarquée dans la carte plastique. Une alternative pour communiquer avec la puce a été récemment mise en œuvre et déployée auprès des consommateurs. Il s’agit d’un protocole radio-fréquence : le protocole NFC pour Near Field Communication, qui ne nécessite donc aucun contact physique avec la carte.

Le micromodule comporte 5 points de contact (les trois autres ne sont pas ou plus utilisés). Le plot Vcc fournit l’alimentation générale du circuit intégré (CI), tandis que le plot Gnd est utilisé comme potentiel de masse (ou Ground, Gnd). Le CI étant un circuit synchrone, un signal d’horloge (CLK) est fourni par le plot de contact Clk, bien que maintenant la majorité des circuits aient un générateur de signaux d’horloge interne pour des raisons de sécurité. Le transfert des données entre le lecteur et la carte à puce est assuré par le contact d’entrée/sortie, I/O (Input/Output). Enfin, le contact Rst (Reset) permet d’envoyer un signal de réinitialisation à la puce lors de son fonctionnement.

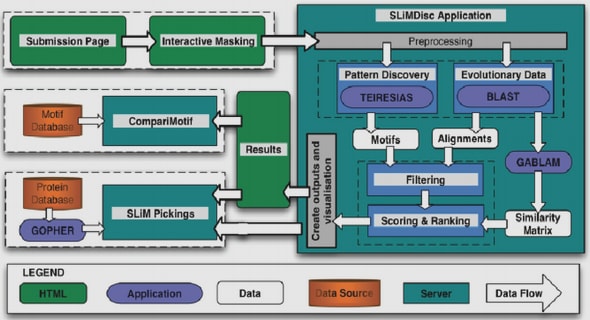

Sa communication avec le lecteur extérieur se fait via l’émetteur récepteur asynchrone universel appelé l’UART (Universal Asynchronous Receiver Transmitter), au moyen des plots de contacts. Elle est également constituée des éléments classiques d’un microcontrôleur, à savoir un microprocesseur (CPU), des mémoires (RAM, ROM et EEPROM) et d’un bloc analogique. Les signaux de données sont transportés dans l’ensemble des éléments du circuit via le bus de données. Un module d’interface radiofréquence (RF) permet la communication avec l’extérieur par la technologie NFC et une antenne. Enfin, les puces conçues pour des applications sécuritaires, intègrent généralement un ou plusieurs processeurs cryptographiques (ou cryptoprocesseurs), permettant de chiffrer plus efficacement et de manière plus sûre des données. Ces éléments primordiaux et les concepts de la cryptographie sont détaillés dans la section suivante.

Le crypto-processeur

Une carte à puce peut contenir des données personnelles et sensibles dont il est primordial d’assurer la sécurité. La sécurisation de ce type de données est devenue un enjeu d’autant plus important que les objets connectés (Internet Of Things), constituant des cibles de choix pour les pirates, se sont multipliés ces dernières années.

L’intégration d’algorithmes cryptographiques au sein des puces est donc devenue incontournable ces dernières années : même les microcontrôleurs dédiés à des applications standards (non sécuritaires) intègrent désormais de tels algorithmes.

L’objectif d’un système sécurisé est d’assurer :

– La confidentialité des données : seules les personnes autorisées peuvent lire les informations chiffrées.

– L’intégrité des données : le message chiffré ne peut pas être modifié ou altéré sans que cela soit perçu par les personnes autorisées.

– L’authenticité des données : les données lues par le destinataire ont bien été envoyées par l’émetteur signant ces données.

– La non-répudiation : l’auteur d’un message codé ne peut pas renier en être la source.

Les algorithmes de chiffrement se basent sur les principes de Kerckhoff [4]. Ces derniers partent du postulat selon lequel toutes les méthodes de chiffrement sont connues de l’ennemi, et affirment donc que la sécurité d’un système cryptographique ne doit reposer que sur la confidentialité des clés de chiffrement et en aucun cas sur la méthode de chiffrement.

La méthode de chiffrement la plus utilisée est le chiffrement symétrique (utilisant la même clé secrète pour le cryptage et décryptage) par bloc. De tels algorithmes se déroulent en général en plusieurs rondes durant lesquelles une sous-clé (dérivée de la clé secrète) est utilisée pour chiffrer le message. Le nombre de rondes dépend du nombre de bits de la clé secrète. Par exemple, les algorithmes AES (Advanced Encryption Standard) à 128bits, 192 bits et 256bits se déroulent en 10, 12 et 14 rondes respectivement. Au terme de la dernière ronde, le message est entièrement crypté.

Le message (ou cyphertext) que l’on souhaite transmettre est d’abord chiffré par un algorithme de cryptage, en utilisant une clé symétrique. Ce message est ainsi chiffré pour être transmis à un tiers, via un canal non sécurisé. Le destinataire du message le décrypte alors en utilisant la même clé.

Des crypto-processeurs matériels sont souvent utilisés pour effectuer les algorithmes cryptographies, pour gérer les clefs et messages cryptographiques et pour implanter les protocoles cryptographiques décrits dans le paragraphe précédent. Ils sont utilisés pour leur flexibilité et leur haute performance et sont donc également les cibles d’attaques logicielles et matérielles dont le but est souvent de révéler les clés secrètes de chiffrement.

Introduction générale |